# INTERFACING TO TE DIGITAL PRESSURE MODULES

The TE series of digital pressure sensors uses the latest CMOS sensor conditioning circuitry (SSC) to create a low cost, high performance digital output pressure (14-bit) and temperature (11-bit) sensor designed to meet the strictest requirements from OEM customers.

The MS45x5DO, 85BSD, 85FBSD, 86BSD, 154BSD, MSP100(DO) and MSP300(DO) are the latest offering from TE to offer digital communication to pressure sensor OEMs.

#### I<sup>2</sup>C AND SPI INTERFACE SPECIFICATIONS

#### 1. I<sup>2</sup>C Interface Specification

The I<sup>2</sup>C interface is a simple 8-bit protocol using a serial data line (SDA) and a serial clock line (SCL) where each device connected to the bus is software addressable by a unique address. For detailed specifications of the I<sup>2</sup>C protocol, see The I<sup>2</sup>C Bus Specification, Version 2.1, January 2000.

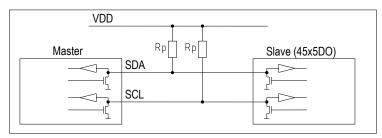

#### 1.1 Interface Connection-External

Bi-directional bus lines are implemented by the devices (master and slave) using open-drain output stages and a pull-up resistor connected to the positive supply voltage. The recommended pull-up resistor value depends on the system setup (capacitance of the circuit or cable and bus clock frequency). In most cases,  $4.7k\Omega$  is a reasonable choice. The capacitive loads on SDA and SCL line have to be the same. It is important to avoid asymmetric capacitive loads.

# I<sup>2</sup>C Transmission Start Condition

Both bus lines, SDA and SCL, are bi-directional and therefore require an external pull-up resistor.

## 1.2 I<sup>2</sup>C Address

The  $I^2C$  address consists of a 7-digit binary value. The factory setting for the  $I^2C$  slave address is 0x28, 0x36 or 0x46 depending on the interface type selected from the ordering information. The address is always followed by a write bit (0) or read bit (1). The default hexadecimal  $I^2C$  header for read access to the sensor is therefore 0x51, 0x6D, 0x8D respectively, based on the ordering information.

#### 1.3 INT/SS Pin

When programmed as an I<sup>2</sup>C device, the INT/SS pin operates as an interrupt. The INT/SS pin rises when new output data is ready and falls when the next I<sup>2</sup>C communication occurs.

#### 1.4 Transfer Sequences

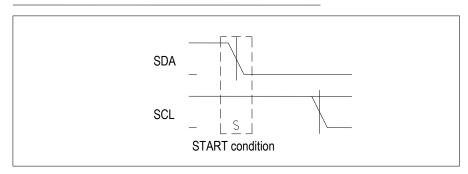

**Transmission START Condition (S)**: The START condition is a unique situation on the bus created by the master, indicating to the slaves the beginning of a transmission sequence (the bus is considered busy after a START).

# I<sup>2</sup>C Transmission Start Condition

A HIGH to LOW transition on the SDA line while SCL is HIGH

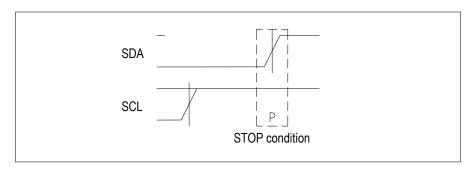

**Transmission STOP Condition (P):** The STOP condition is a unique situation on the bus created by the master, indicating to the slaves the end of a transmission sequence (the bus is considered free after a STOP).

# I<sup>2</sup>C Transmission Stop Condition

A LOW to HIGH transition on the SDA line while SCL is HIGH

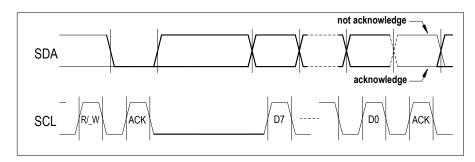

Acknowledge (ACK) / Not Acknowledge (NACK): Each byte (8 bits) transmitted over the  $I^2C$  bus is followed by an acknowledge condition from the receiver. This means that after the master pulls SCL low to complete the transmission of the 8th bit, SDA will be pulled low by the receiver during the 9th bit time. If after transmission of the 8th bit the receiver does not pull the SDA line low, this is considered to be a NACK condition.

If an ACK is missing during a slave to master transmission, the slave aborts the transmission and goes into idle mode.

# I<sup>2</sup>C Acknowledge / Not acknowledge

Each byte is followed by an acknowledge or a not acknowledge, generated by the receiver

#### 1.5 Data Transfer Format

Data is transferred in byte packets in the I<sup>2</sup>C protocol, which means in 8-bit frames. Each byte is followed by an acknowledge bit. Data is transferred with the most significant bit (MSB) first.

A data transfer sequence is initiated by the master generating the Start condition (S) and sending a header byte. The I<sup>2</sup>C header consists of the 7-bit I<sup>2</sup>C device address and the data direction bit (R/\_W).

The value of the R/\_W bit in the header determines the data direction for the rest of the data transfer sequence. If R/W = 0 (WRITE), the direction remains master-to-slave, while if R/W = 1 (READ), the direction changes to slave-to-master after the header byte.

#### 1.6 Command Set and Data Transfer Sequences

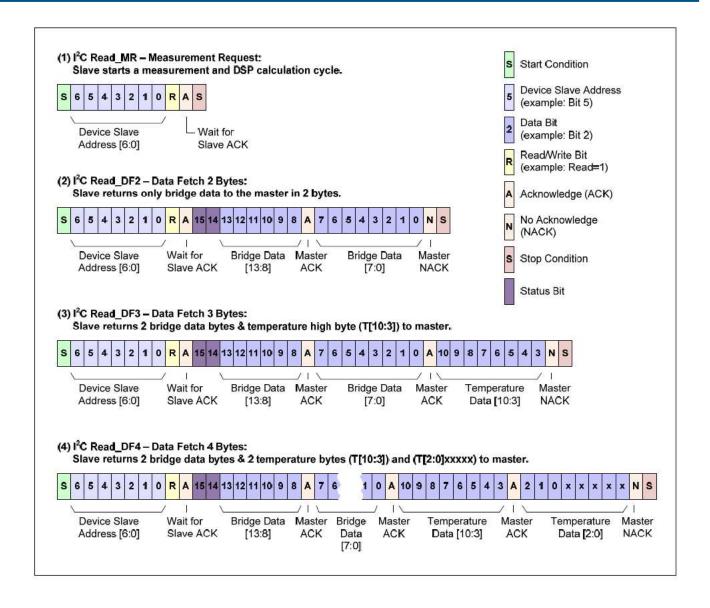

The  $I^2C$  master command starts with the 7-bit slave address with the 8th bit = 1 (READ). The sensor acts as the slave and sends an acknowledge (ACK) indicating success. The sensor has four  $I^2C$  read commands: Read\_MR, Read\_DF2, Read\_DF3, and Read\_DF4. Figure 1.6 shows the structure of the measurement packet of the four  $I^2C$  read commands, which are explained in sections 1.6.1.

#### 1.6.1 Figure 1.6 – I<sup>2</sup>C Measurement Packet Readsl<sup>2</sup>C Read DF (Data Fetch)

For Data Fetch commands, the number of data bytes returned by the sensor, is determined when the master sends the NACK and stop condition. For the Read\_DF3 data fetch command (Data Fetch 3 Bytes; see example 3 in Figure 1.6), the sensor returns three bytes in response to the master sending the slave address and the READ bit (1): two bytes of bridge data with the two status bits as the MSBs and then 1 byte of temperature data (8-bit accuracy). After receiving the required number of data bytes, the master sends the NACK and stop condition to terminate the read operation. For the Read\_DF4 command, the master delays sending the NACK and continues reading an additional final byte to acquire the full corrected 11-bit temperature measurement. In this case, the last 5 bits of the final byte of the packet are undetermined and should be masked off in the application. The Read\_DF2 command is used if corrected temperature is not required. The master terminates the READ operation after the two bytes of bridge data (see example 2 in Figure 1.6).

The two status bits (Bit 15 and Bit 14) give an indication of stale or valid data depending on their value. A returned value of 00 indicate "normal operation and a good data packet" while a returned value of 10 indicates "stale data that has been already fetched". See section 1.7 for additional details. Users that use "status bit" polling should select a frequency slower than 20% more than the update time.

## **INTERFACING TO MEAS DIGITAL PRESSURE MODULES**

#### 1.7 Status Bits and Diagnostic Features

The table below summarizes the status bits conditions indicated by the 2 MSBs (Bit (15:14) of I<sup>2</sup>C data packet, S(1:0) of SPI data packet of the bridge high byte data.

Table 1: Status Bits Encoding

| Status Bits (2 MSB of Output Data Packet) | Definition                                                      |

|-------------------------------------------|-----------------------------------------------------------------|

| 00                                        | Normal Operation. Good Data Packet                              |

| 01                                        | Reserved                                                        |

| 10                                        | Stale Data. Data has been fetched since last measurement cycle. |

| 11                                        | Fault Detected                                                  |

The SSC is has on board diagnostic features to ensure robust system operation in the most "mission-critical" applications. A status bit value of "11" indicates a fault condition in the SSC or sensing element. All diagnostics are detected in the next measurement cycle and reported in the subsequent data fetch. Once a diagnostic is reported, the diagnostic status bits will not change unless both the cause of the diagnostic is fixed and a power-on-reset is performed.

#### 1.8 I<sup>2</sup>C Protocol Differences

There are three differences in the described above protocol compared with original I<sup>2</sup>C protocol:

- Sending a start-stop condition without any transitions on the SCL line (no clock pulses in between) creates a communication error for the next communication, even if the next start condition is correct and the clock pulse is applied. An additional start condition must be sent, which results in restoration of proper communication.

- The restart condition a falling SDA edge during data transmission when the SCL clock line is still high creates the same situation. The next communication fails, and an additional start condition must be sent for correct communication.

- A falling SDA edge is not allowed between the start condition and the first rising SCL edge. If using an I<sup>2</sup>C address with the first bit 0, SDA must be held down from the start condition through the first bit.

#### 2. SPI Interface Specification

SPI is a general-purpose synchronous serial interface. During an SPI transfer, transmit and receive data is simultaneously shifted out and in serially. A serial clock line synchronizes the shifting and sampling of the information on two serial data lines.

SPI devices communicate using a master-slave relationship. Due to its lack of built-in device addressing, SPI requires more effort and more hardware resources than I<sup>2</sup>C when more than one slave is involved. But SPI tends to be simpler and more efficient than I<sup>2</sup>C in point-to-point (single master, single slave) applications for the very same reason; the lack of device addressing means less overhead.

The SPI interface is programmed for falling-edge MISO change.

#### **INTERFACING TO MEAS DIGITAL PRESSURE MODULES**

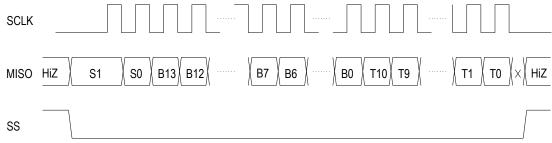

#### 2.1 SPI Read DF (Data Fetch)

The SPI interface will have data change after the falling edge of SCLK. The master should sample MISO on the rise of SCLK. The entire output packet is 4 bytes (32 bits). The high bridge data byte comes first, followed by the low bridge data byte. Then 11 bits of corrected temperature (T[10:0]) are sent: first the T[10:3]byte and then the {T[2:0],xxxxx} byte. The last 5 bits of the final byte are undetermined and should be masked off in the application. If the user only requires the corrected bridge value, the read can be terminated after the 2nd byte. If the corrected temperature is also required but only at an 8-bit resolution, the read can be terminated after the 3rd byte is read.

Packet =  $[{S(1:0),B(13:8)},{B(7:0)},{T(10:3)},{T(2:0),xxxxx}]$  Where

S(1:0) = Status bits of packet (normal, command, busy, diagnostic)

B(13:8) = Upper 6 bits of 14-bit bridge data.

B(7:0) = Lower 8 bits of 14-bit bridge data.

T(10:3) = Corrected temperature data (if application does not require corrected temperature, terminate read early)

T(2:0),xxxxx =. Remaining bits of corrected temperature data for full 11-bit resolution

HiZ = High impedance

Figure 2.2 – SPI Output Packet with Falling Edge SPI Polarity

#### **TIMING DIAGRAMS**

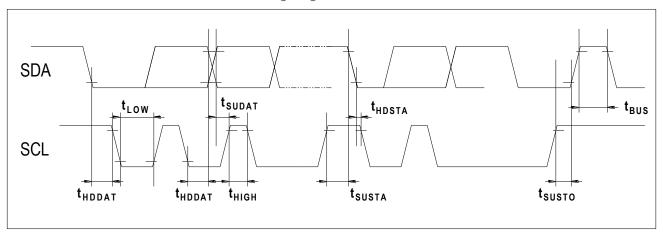

#### I<sup>2</sup>C INTERFACE PARAMETERS

| PARAMETERS                                      | SYMBOL           | MIN | TYP | MAX | UNITS |

|-------------------------------------------------|------------------|-----|-----|-----|-------|

| SCLK CLOCK FREQUENCY                            | fscL             | 100 |     | 400 | KHz   |

| START CONDITION HOLD TIME RELATIVE TO SCL EDGE  | thdsta           | 0.1 |     |     | uS    |

| MINIMUM SCL CLOCK LOW WIDTH 1                   | tLOW             | 0.6 |     |     | uS    |

| MINIMUM SCL CLOCK HIGH WIDTH 1                  | tніgн            | 0.6 |     |     | uS    |

| START CONDITION SETUP TIME RELATIVE TO SCL EDGE | tsusта           | 0.1 |     |     | uS    |

| DATA HOLD TIME ON SDA RELATIVE TO SCL EDGE      | thddat           | 0   |     |     | uS    |

| DATA SETUP TIME ON SDA RELATIVE TO SCL EDGE     | tsudat           | 0.1 |     |     | uS    |

| STOP CONDITION SETUP TIME ON SCL                | tsusто           | 0.1 |     |     | uS    |

| BUS FREE TIME BETWEEN STOP AND START CONDITION  | t <sub>BUS</sub> | 2   |     |     | uS    |

<sup>&</sup>lt;sup>1</sup> COMBINED LOW AND HIGH WIDTHS MUST EQUAL OR EXCEED MINIMUM SCL PERIOD.

## **I2C Timing Diagram**

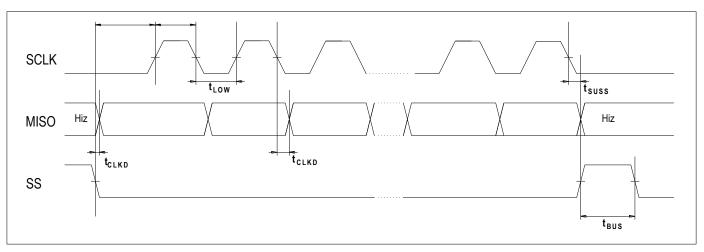

#### SPI INTERFACE PARAMETERS

| PARAMETERS                                | SYMBOL            | MIN | TYP | MAX | UNITS |

|-------------------------------------------|-------------------|-----|-----|-----|-------|

| SCLK CLOCK FREQUENCY                      | f <sub>SCL</sub>  | 50  |     | 800 | KHz   |

| SS DROP TO FIRST CLOCK EDGE               | t <sub>HDSS</sub> | 2.5 |     |     | uS    |

| MINIMUM SCL CLOCK LOW WIDTH 1             | t <sub>LOW</sub>  | 0.6 |     |     | uS    |

| MINIMUM SCL CLOCK HIGH WIDTH 1            | t <sub>HIGH</sub> | 0.6 |     |     | uS    |

| CLOCK EDGE TO DATA TRANSITION             | t <sub>CLKD</sub> | 0   |     | 0.1 | uS    |

| RISE OF SS RELATIVE TO LAST CLOCK EDGE    | t <sub>suss</sub> | 0.1 |     |     | uS    |

| BUS FREE TIME BETWEEN RISE AND FALL OF SS | t <sub>BUS</sub>  | 2   |     |     | uS    |

<sup>&</sup>lt;sup>1</sup> COMBINED LOW AND HIGH WIDTHS MUST EQUAL OR EXCEED MINIMUM SCLK PERIOD.

### **SPI TIMING DIAGRAM**

#### **INTERFACING TO MEAS DIGITAL PRESSURE MODULES**

#### **NORTH AMERICA**

Measurement Specialties, Inc., a TE Connectivity company 45738 Northport Loop West Fremont, CA 94538 Tel: +1 800 767 1888 Fax: +1 510 498 1578 customercare.frmt@te.com

#### **EUROPE**

MEAS Switzerland Sarl, a TE Connectivity company Ch. Chapons-des-Prés 11 CH-2022 Bevaix Tel: +41 32 847 9550 Fax: +41 32 847 9569 customercare.bevx@te.com

# ASIA

Measurement Specialties (China) Ltd., a TE Connectivity company No. 26 Langshan Road Shenzhen High-Tech Park (North) Nanshan District, Shenzhen, 518057 China

Tel: +86 755 3330 5088 Fax: +86 755 3330 5099 customercare.shzn@te.com

#### te.com/sensorsolutions

Measurement Specialties, Inc., a TE Connectivity company.

Measurement Specialties (MEAS), American Sensor Technologies (AST), TE Connectivity, TE Connectivity (logo) and EVERY CONNECTION COUNTS are trademarks. All other logos, products and/or company names referred to herein might be trademarks of their respective owners.

The information given herein, including drawings, illustrations and schematics which are intended for illustration purposes only, is believed to be reliable. However, TE Connectivity makes no warranties as to its accuracy or completeness and disclaims any liability in connection with its use. TE Connectivity's obligations shall only be as set forth in TE Connectivity's Standard Terms and Conditions of Sale for this product and in no case will TE Connectivity be liable for any incidental, indirect or consequential damages arising out of the sale, resale, use or misuse of the product. Users of TE Connectivity products should make their own evaluation to determine the suitability of each such product for the specific application.

© 2016 TE Connectivity Ltd. family of companies All Rights Reserved.